【エグゼクティブ・サマリー】

- IntelがイーロンマスクのTeraFabプロジェクトに正式参画し、ロジック・メモリ・先進パッケージングの垂直統合による年間1テラワット(1 TW/year)の計算資源供給という前例のない目標に向けてIntel Foundryのリソースを投入する

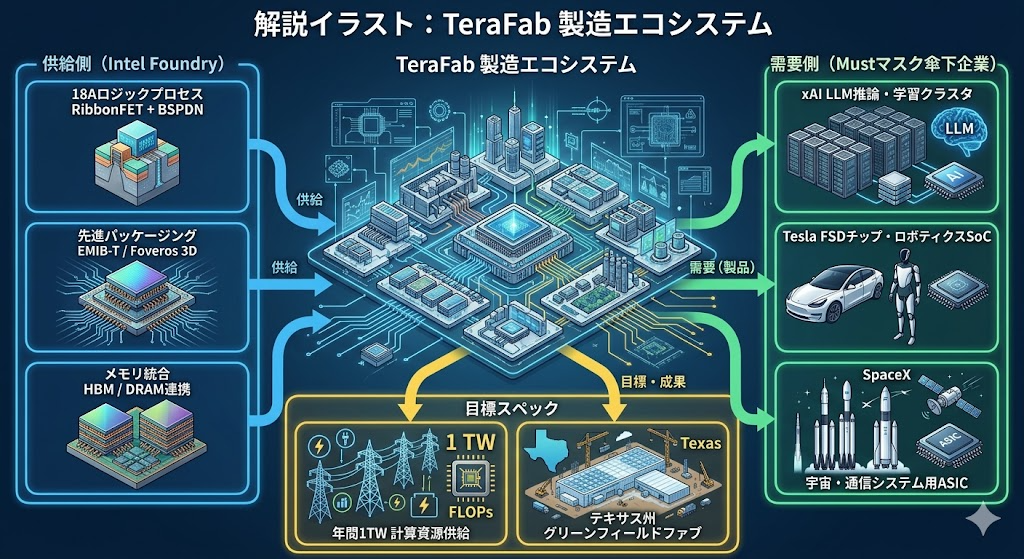

- TeraFabは単なるウェーハ供給契約を超え、Tesla・SpaceX・xAIの次世代AIおよびロボティクスワークロード向けにカスタムシリコンを設計・製造・パッケージングまで一気通貫で賄う製造エコシステムの再構築を目指す

- 発表はX上のポストのみで詳細に乏しく、法的拘束力や資本構造は未開示だが、Intel Foundryが2025年通期で103億ドルの営業損失を計上している状況下で、同部門の商用妥当性を証明するための戦略的意義は極めて大きい

既存テクノロジーの限界と課題

現代のAI・ロボティクスインフラが直面しているボトルネックは、単純なチップ性能の問題ではなく、半導体サプライチェーン構造そのものに起因している。

物理的・構造的な課題

- リードタイムの長期化:ロジックチップ(TSMC)、HBMメモリ(SK Hynix)、先進パッケージング(外部OSAT)をそれぞれ別拠点で製造・調達する現行モデルでは、最終製品の完成まで数ヶ月単位のリードタイムが発生する

- インターコネクト帯域のボトルネック:異なるファウンドリで製造されたダイを後工程で接合する場合、チップ間インターコネクトの帯域密度と信号完全性が制約となり、特にLLM推論に必要なメモリ帯域幅の確保が難しくなる

- 電力・冷却スケールの限界:xAIのColossusクラスタのように数万GPU規模のクラスタを構築する場合、既存のデータセンターインフラでは電力密度と排熱処理が物理的限界に近づいている。現行の空冷・水冷の組み合わせでは、ラック密度の向上に限界が生じている

- TSMC一極集中リスク:先端ロジックの製造能力がTSMCに極度に集中しており、Tesla・SpaceX・xAIのような急成長する需要側が独自のシリコン調達戦略を持てない構造的脆弱性がある

- カスタムシリコン開発の摩擦:汎用GPUではなく特定ワークロードに最適化したASICを開発しようとした場合、設計会社・ファウンドリ・パッケージングベンダーの三者間の調整コストが開発速度を大きく制約する

ニュースの核心とアーキテクチャの優位性

TeraFabとは何か——「工場」ではなく「製造パラダイムの再定義」

“Terafab represents a step change in how silicon logic, memory and packaging will get built in the future.” — Lip-Bu Tan(Intel CEO)、X投稿より

IntelのCEO、リップ・ブー・タン氏の発言が示す通り、TeraFabは既存の半導体製造業の段階的改善(incremental improvement)ではなく、ステップチェンジとして位置づけられている。

公式定義によれば、TeraFabは「ロジック、メモリ、先進パッケージングを一つの屋根の下に集約する」ことを掲げる。これはモノリシックな垂直統合ファブの概念であり、既存の水平分業モデルとは根本的に異なる設計思想だ。

IntelがTeraFabにもたらす技術的資産

- 18Aプロセスノード:RibbonFET(GAA型トランジスタ)とBackside Power Delivery Network(BSPDN)を採用した次世代プロセス。電力効率とトランジスタ密度の両面でTSMCのN2と真っ向から競合する位置づけ

- EMIB-T(Embedded Multi-die Interconnect Bridge – T世代):Intel Foundryの先進パッケージング技術の最新ロードマップに位置する規格。最大120×180mmのパッケージサイズに対応し、38個以上のシリコンブリッジと12個以上のレティクルサイズ・ダイを単一パッケージ内に収容可能。これにより、複数のロジックダイとHBMをワンパッケージで集積するGigantic Multi-Chip Module(MCM)の実現が視野に入る

- Foveros 3Dスタッキング:ダイをFace-to-Faceでスタックし、μbump経由でダイ間通信を行う3D実装技術。チップ間の通信レイテンシを大幅に削減し、帯域幅密度を向上させる

1 TW/yearという目標値の物理的スケール感

年間1テラワットの計算リソースという目標は、現実的にどの程度の規模感なのか。

現行のNVIDIA H100 GPUは、単体でのTDP(熱設計電力)が700W前後だ。仮に平均消費電力を500Wとして1 TW/yearを連続稼働で供給しようとすると、単純計算で約20億個のH100相当GPUが必要となる——これは当然単純計算の極論だが、目標が「累積生産能力」であることを考えると、数十億ドル規模の半導体生産設備への投資が前提となる。

TeraFabがテキサス州にグリーンフィールドのファブ建設を進めていることも、この規模の野心を裏付けている。

提携の構造的曖昧さとその読み方

注目すべきは、今回の発表にプレスリリースもSEC提出書類も存在しないという点だ。X上のポストのみが公式の発表手段として使われており、法的な拘束力や出資比率、製造割り当て等は一切開示されていない。

これはいくつかの解釈を許す:

- コンソーシアム型:Intel、Tesla、SpaceX、xAIが容量プールを共有する仮想的な生産エコシステム。既存のウェーハ供給契約の上位版

- 共同投資型ファブ:複数社が資本を拠出し、統一プロセス技術で稼働する専用ラインを設ける形態

- カスタムシリコン開発契約:Intelが各社の特定ワークロード向けにASICを設計・製造する、実質的な受託開発モデル

Intel Foundryが2025年通期で売上高178億ドルに対して103億ドルの営業損失を計上している現状を踏まえると、TeraFabとの連携は18Aプロセスの初期顧客獲得と稼働率改善という財務的合理性も強く働いている。

【比較表】従来アーキテクチャとのスペック比較

| 比較項目 | 従来モデル(水平分業・外部調達) | TeraFab構想(垂直統合型) |

|---|---|---|

| 製造体制 | ロジック(TSMC)、メモリ(SK Hynix等)、パッケージング(外部OSAT)を別々に調達 | ロジック・メモリ・パッケージングを単一施設または緊密連携で集約 |

| リードタイム | 数ヶ月〜半年超(各工程間の物流・調整が発生) | 目標:大幅短縮(工程間移動距離の最小化) |

| パッケージング能力 | 従来COWoS:パッケージサイズ・ブリッジ数に制約あり | EMIB-T:120×180mm、ブリッジ38個以上、ダイ12個以上 |

| 計算資源供給目標 | 個社別の調達契約に依存(数百MW規模) | 年間1TW(テラワット)の計算資源供給 |

| カスタムシリコン対応 | 設計・製造・パッケージングの三者調整が必要 | 一気通貫での最適化が理論上可能 |

| 地政学的リスク | TSMC(台湾)への依存度が極めて高い | テキサス州グリーンフィールドファブ(米国内) |

| プロセスノード | TSMC N3/N2主体 | Intel 18A(RibbonFET + BSPDN)を軸に展開 |

【図解】技術アーキテクチャ・関係図

【考察】ITエコシステム・業界へのインパクト

1. TSMC一強時代への本格的な楔

TSMCは現在、先端ロジック半導体の受託製造において事実上の独占的地位を持つ。IntelのTeraFab参画が持つ最大の産業的意義は、この構造に対する対抗軸の形成だ。

NVIDIA・AMD・Qualcommのような大手ファブレス企業にとって、Intelが実際に競争力ある先端ファウンドリとして機能し始めれば、TSMCとの価格交渉力が回復する。特に先端パッケージング(CoWoS、SoIC)はTSMCがほぼ独占していた領域であり、EMIB-TがこのポジションにIntel側から迫ることの技術的・商業的意味は大きい。

2. AI電力インフラへの波及効果

年間1TWという目標は、半導体製造のスループットの話だけでなく、そのチップを動かすための電力・冷却インフラの議論と不可分だ。

xAIがメンフィスで稼働させているColossusクラスタはすでに200MWを超える電力を消費しているとされる。これをテラワット規模に引き上げるとなれば、直接液冷(DLC)や液浸冷却(Immersion Cooling)の大規模展開、さらには専用変電設備の整備が前提となる。データセンター電力インフラ企業(Vertiv等)への長期的な需要下支え効果は、Geminiの考察が指摘する通り現実的なシナリオだ。

3. 地政学リスクの再配置

TeraFabがテキサス州でのグリーンフィールドファブ建設を進めていることは、台湾有事リスクへのヘッジという観点から米国政府・防衛産業の強い支持を受けやすい。CHIPS Act補助金の文脈でも、国内製造拠点の強化に合致するため、政策的追い風は続くと見られる。

4. Intel Foundryの財務的転換点となるか

103億ドルという巨額の営業損失を抱えるIntel Foundryが、TeraFabという大型プロジェクトの「プリファードパートナー」として名を連ねることは、18Aプロセスの歩留まり改善と顧客信頼性の両立という最大の課題に取り組む正当性を社内外に示す。ただし、今回の発表が実際の製造受注に転換するまでには、18Aの量産実績という具体的な裏付けが不可欠となる。

まとめ

今回の発表で最も注目すべきは、その内容の曖昧さそのものが持つ戦略的メッセージ性だ。法的拘束力も資本構造も開示しないまま、IntelとイーロンマスクがX上でパートナーシップを宣言するというやり方は、市場へのシグナリングとして機能している——IntelはTSMCの代替足り得るという意思表明、そしてTeraFabは実在する調達先を持つプロジェクトであるという信頼性の補強だ。

EMIB-Tによる120×180mmパッケージという技術仕様と、年間1TWという計算資源目標の間には、まだ埋めるべき技術的・財務的ギャップが大きく存在する。次の判断材料は、18Aの外部顧客向け量産出荷実績と、TeraFabによるテキサスファブへの実際の投資規模の開示だ。

引用元記事・補足資料

Intel joins Elon Musk’s TeraFab project — ‘Intel is proud to join the Terafab project with SpaceX, xAI, and Tesla to help refactor silicon fab technology’:本記事のメインソース。Intel公式X投稿の引用とTom’s Hardwareによる業界分析を含む。IntelCEOおよびリップブータン氏の発言が収録されている。

Intel reportedly in talks with Google and Amazon over advanced packaging:EMIB-Tの技術仕様(120×180mmパッケージ、38ブリッジ以上)およびIntel Foundry 2025年通期決算データ(売上高178億ドル、営業損失103億ドル)の出典。先進パッケージング技術の競争力の根拠として参照。

コメント